# **HP 1670G Series Benchtop Logic Analyzers**

Listing MPC860 BUS Run Analyzer Invasm Options Print Markers Acquisition Time Off MPC821/860 Inverse Assembler ADDR Time. Label> 10.=decimal, %10=binary Absolu Base> Symbol 10=hex. indie:fillup+0108 indie:fillup+010C indie:fillup+0110 1032149 1032153 indie:fillup+0114 indie:fillup+0118 1032157 Indie:fillup+011C indie:fillup+0124 \_\_\_\_1032165 indie:fillup+0128 indie:fillup+012C indie:fillup+0130 indie:fillup+0134 indie:fillup+0138 pgm 54E710\*\* indie:fillup+013C

2 M deep acquisition memory allows analysis of long periods of target system execution.

## Key Specifications and Characteristics for HP 1670G Series Benchtop Logic Analyzers

| Model                                    | 1670G                                                                                                                                                                     | 1671G                                                                                                                                                                                                 | 1672G                                              | 1673G |  |  |  |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------|--|--|--|

| Channels                                 | 136                                                                                                                                                                       | 102                                                                                                                                                                                                   | 68                                                 | 34    |  |  |  |

| State Speed                              | 135 MHz                                                                                                                                                                   |                                                                                                                                                                                                       |                                                    |       |  |  |  |

| Timing Speed                             | 250 MHz on all channels, 500 MHz on half channels                                                                                                                         |                                                                                                                                                                                                       |                                                    |       |  |  |  |

| Memory Depth<br>Option 001<br>Option 002 | 256K mem                                                                                                                                                                  |                                                                                                                                                                                                       | 128K half chan<br>channel timin<br>annel timing)   |       |  |  |  |

| Setup/Hold Time                          | 3.5/0 ns to 0/3.5 ns adjustable in 500-ps increments                                                                                                                      |                                                                                                                                                                                                       |                                                    |       |  |  |  |

| Probe Input R & C                        | 100 kΩ, 8pF                                                                                                                                                               |                                                                                                                                                                                                       |                                                    |       |  |  |  |

| Triggering                               | 2 edge & q<br>includes 2<br>graphical                                                                                                                                     | Up to 12 sequence levels with 10 pattern terms, 2 edge & glitch terms, 2 ranges and timers. Also includes 23 predefined trigger macros with graphical representations and plain language descriptions |                                                    |       |  |  |  |

| I/O Standards                            | Ethernet L<br>HP-IB, Pa<br>DIN mous                                                                                                                                       |                                                                                                                                                                                                       | rd ports                                           |       |  |  |  |

| Oscilloscope<br>Option 003               | Number of scope channels: 2<br>Scope bandwidth: 500 MHz<br>Scope sample rate: 2 Gsa/s<br>Scope vertical resolution: 8 bits<br>Scope memory depth: 32K samples per channel |                                                                                                                                                                                                       |                                                    |       |  |  |  |

| Pattern Generator<br>Option 004          | Max clock                                                                                                                                                                 |                                                                                                                                                                                                       | erator channel<br>1Hz (32 Ch), 20<br>3,048 vectors |       |  |  |  |

| Training Kit<br>Option 005               | Includes a training guide, example setup and data files, and a credit-card-sized target system board                                                                      |                                                                                                                                                                                                       |                                                    |       |  |  |  |

## **Key Literature**

Both of the following items are also available from the web site: www.hp.com/go/LAbenchtops.

HP 1670G Series Technical Specifications, p/n 5968-6421EN/EUS HP Digital Design and Debug Tools Catalog, p/n 5968-6355EN/EUS CD-ROM "Logic Analysis and Emulation Solutions" version 5.0, p/n 5965-7502E

#### **Ordering Information**

| Model                                                                                     | 1670G              | 1671G                    | 1672G              | 1673G              |

|-------------------------------------------------------------------------------------------|--------------------|--------------------------|--------------------|--------------------|

| Channels                                                                                  | 136                | 102                      | 68                 | 34                 |

| Base Price                                                                                | \$15,000           | \$12,500                 | \$10,000           | \$7,500            |

| Memory Options (choo<br>Option 001 (256K)<br>Option 002 (2M)                              | +\$4000<br>+\$8000 | +\$3000<br>+\$6000       | +\$2000<br>+\$4000 | +\$1000<br>+\$2000 |

| Companion Tools (choose 1 or none) Option 003 (Scope) +\$7000 Option 004 (PatGen) +\$3500 |                    | e)<br>+\$7000<br>+\$3500 | +\$7000<br>+\$3500 | +\$7000<br>+\$3500 |

| Training Kit<br>Option 005                                                                | +\$200             | +\$200                   | +\$200             | +\$200             |

## The HP 1664A Entry Level Logic Analyzer

The HP 1664A logic analyzer offers many of the popular features of the HP 1670G series at an entry-level price. Its features include: 50 MHz state analysis, 500 MHz timing analysis, 34 acquisition channels and 4K samples per channel memory depth. The HP 1664A uses a gray scale display and is compatible with a wide variety of processor specific inverse assemblers. The HP 1664A is priced at \$5,000. See the technical data sheet or web site for more information regarding the HP 1664A.

HP 1670G HP 1671G HP 1672G

HP 1673G

#### 418

# **HP 1670G Series Benchtop Logic Analyzers**

HP 1670G

HP 1671G HP 1672G HP 1673G **HP 1664A**

specific application Simplify capture and analysis of complex events with up to 2M deep memory

Tailor cost-effective solutions to match your

- View analog and digital signals simultaneously with the optional twochannel, 500 MHz oscilloscope

- Stimulate circuits and simulate missing components with the optional pattern generator capability

## Get Personalized Power with a Logic Analyzer **Built for Your Unique Needs**

The HP 1670G Series logic analyzers offer cost-effective 135 MHz state analysis and timing analysis at speeds up to 500 MHz. The high-speed acquisition memory can be configured for depths up to 2M samples over as many as 136 acquisition channels. An optional 2-channel, 500 MHz oscilloscope or a 32-channel pattern generator capable of up to 200 MVector/s can be added to the unit to customize it for signal integrity or stimulus-response applications. Never before has so much measurement power been available in such an affordable package.

You'll make productive use of all the measurement power, too. A commonsense user interface helps you solve your design problems faster, and the ability to view processor mnemonics and waveforms simultaneously makes it easier to see cause/effect relationships in your system. Navigating through the user interface is made simple via a choice of either mouse or front-panel operation. An optional keyboard is also available. The color flat-panel display will help you find information quickly.

Graphical trigger macros assist in making powerful measurements. Trigger setups can be selected from a categorized list of trigger macros. Each macro is shown in a graphical form and has a written description. Macros can be chained together to form a custom trigger sequence.

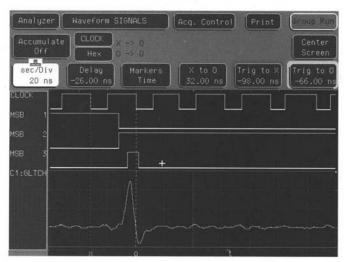

Optional built-in oscilloscope allows correlation of timing, state, and analog signals, to facilitate identification of glitches.

### An Excellent Toolset for Hardware Development

Some of the tougher hardware problems can be found only with the digital triggering capabilities of a logic analyzer and solved only with the analog resolution of an oscilloscope. That's why a built-in, 500 MHz, 2-Gsa/s oscilloscope that can be triggered by the logic analyzer may be added to any model. Now, you can see what bus lines really look like at critical moments.

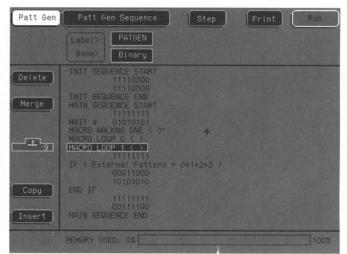

The optional pattern generator capability allows you to functionally test your digital design. You can stimulate the design under test and see how it responds to specific signals or clock speeds. You can also use the pattern generator to substitute for missing subsystems. The data captured with the state or timing analyzer can then be used to verify correct operation.

## Get the Whole Picture with Deep Memory

Deep memory can be a valuable logic analyzer feature for solving difficult or poorly understood problems in embedded microprocessor systems. It saves time you might otherwise spend taking multiple traces to piece together a complete picture of prototype behavior. Deep memory can also reduce the need to set up multilevel triggers because you don't have to be as precise about the data you capture. All models in the HP 1670G series can be configured to have up to 2M samples of memory depth.

Optional 32-channel pattern generator allows stimulation of subsystems with realistic signals before the entire system is ready for testing.

10